先行控制

先行控制实质上是缓冲技术和预处理技术相结合的结果。通过对指令流和数据流的预处理和缓冲,能够儘量使指令分析器和指令执行部件独立地工作,并始终处于忙碌状态。先行控制技术很好地解决了指令分析器和主记忆体之间速度不匹配的问题,能够很好地解决对于控制相关、指令相关、通用暂存器相关和变址相关等问题。

基本介绍

- 中文名:先行控制

- 外文名:advanced control

- 领域:计算机

- 组成:三个独立的控制器、四个缓冲栈

- 关键技术:缓冲技术、预处理技术

- 套用:解决控制相关、指令相关等问题

处理机结构

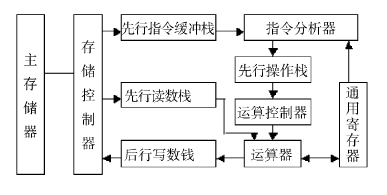

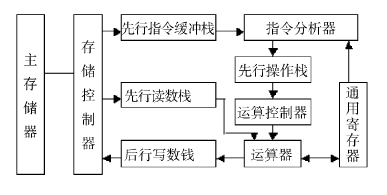

先行控制的处理机结构(如图1所示)包括三个独立的控制器和四个缓冲栈。其中,控制器分别为:存储控制器、指令分析器、运算控制器;缓冲栈分别为:先行指令缓冲栈、先行读数栈、先行操作栈、后行写数栈。 图1 採用先行控制技术的处理机构

图1 採用先行控制技术的处理机构

图1 採用先行控制技术的处理机构

图1 採用先行控制技术的处理机构先行控制是指在处理机内部设定一定容量的指令缓冲栈,把指今分折器所需要的指令事先取到指令缓冲栈中,而不必访问主存储器。这样,就能够使取指令、分析指令和执行指令重叠起来执行。如果指令分析器每次都能够在先行指令缓冲栈中得到,则取指令只需要很短的时间就能够完成,因此,可以把指令与分析指令合併到一起,从而构成图2所示的一次重叠执行方式。

如果分析指今和执行指今所需要的时间都是t,则採用一次重叠执行方式连续执行n条指令所需要的时间为:T=(1+n)t。 图2

图2

图2

图2组成元素介绍

缓冲栈

先行指令缓冲栈作为主存储器与指令分析器之间的一个缓冲部件,用它来平滑主存储器和指令分析器的工作。当指令分析器分析某一条指令所需要的时间比较长,或者主存储器有空闲时,就从主存储器中多取出几条指令存放在先行指令缓冲栈中。而当指令分析器分析指令很快,或者主存储器比较忙时,指令分析器也能够从先行指令缓冲栈中得到所需要的指令。

指令分析器

指令分析器对已经存放在先行指令缓冲栈里的指令进行预处理,把处理机后的指令送入先行操作栈。对于无条件转移及条件转移等程式控制指令,一般在指令分析器中就能够直接执行。各种运算型指令、移位指令、数据传送指令等都要先处理成暂存器-暂存器型(RR型指令),然后送入先行操作栈。为了与指令系统中原有的RR型指令相区别,通常把送入先行操作栈中的指令称为RR*型指令。

先行操作栈

先行操作栈是指令分析器和运算控制器之间的一个缓冲存储器。指令分析器每预处理完一条指令,就把形成的RR*型指令送入先行操作栈,使得指令分析器能够继续对后续的指令进行预处理。每当运算器执行完一条RR*型指令,就由运算控制器从先行操作栈中取出下一条RR*型指令。有了这个缓冲存储器,指令分析器和运算器就能够各自完成独立的工作。先行操作栈採用先进先出方式工作,它由一个先行指令暂存器堆和有关控制逻辑等组成。先行读数栈是主存储器与运算器之间的一个缓冲存储器,用来平滑运算器与主存储器的工作。

先行读数栈

先行读数栈由一个缓冲暂存器和有关控制逻辑等组成。每一个缓冲暂存器由三个部分组成,包括先行地址缓冲暂存器、先行运算元缓冲暂存器和标誌栏位。每当先行地址缓冲暂存器收到从指令分析器中送来的有效地址,就把地址的有效标誌置位,并开始向主存储器申请读运算元。从主存储器读出的运算元可以存放在先行读数栈的运算元缓冲暂存器中,也可以覆盖掉原来的先行地址暂存器中的地址,同时要置位数据有效标誌。先行读数栈一般也採用先进先出方式工作。设定了先行读数栈后,运算器能够直接从先行读数栈中取得所需要的运算元,而不必等待访问主存储器。这样,指令的执行速度就能够大大加快。

后行写数栈

后行写数栈是主存储器与运算器之间的一个缓冲存储器。如果在指令分析器中遇到向主存储器的“写数”指令,则把形成的有效地址送入后行写数栈的后行地址缓冲暂存器中,并把预处理好的RR*型指令送入先行操作栈。当然,这条RR*型指令中的目标暂存器就是后行写数栈的缓冲暂存器编号。当运算器执行这条RR*型写数指令时,只要把写到主存中去的数据送到后行写数栈的后行数据缓冲暂存器中即可,由后行写数栈负责把数据写回到主存储器。这样,运算器不必等待数据写回到主存,就可以继续执行后行的指令。

原理

1、在主存空闲时,即从主存中取出指令放入先行指令缓冲栈,以供指令分析器使用。预取先行指令缓冲栈遵循先进先出。指令分析器对缓冲栈中的指令进行预处理,并送入先行操作栈。

2、对于运算类的指令--则要处理成RR型的指令。如果指令本身就是RR型,则不作任何处理;如果是RS型,则分析器计算出运算元有效地之后送入先行读数栈或后行写数栈的地址暂存器,并将对应的地址暂存器的编号代替指令中的主存地址后送入先行操作栈;如果是RI型,则将立即数送入先行读数栈的运算元暂存器,并用此暂存器的编号代替指令中的立即数栏位。这样,所有的运算类指令执行时都将访问暂存器,加快运算速度。

3、每当先行读数栈收到分析器送来的有效地之后,即将地址有效标誌位置位,并向主存申请读运算元,取得的运算元放入对应的先行运算元缓冲暂存器中,并置数据有效标誌位,做废刚才的地址有效标誌位,以供相应的指令使用运算元。

4、每当后行写数栈收到分析器送来的有效地之后,即将地址有效标誌位置位;这样,当相应的运算类指令执行完毕后不再马上写主存,而是先送入相应的后行写数据缓冲暂存器中,并置数据有效标誌位。控制器自动根据相应的后行写地址缓冲暂存器中的地址向主存发出写请求。

4、每当后行写数栈收到分析器送来的有效地之后,即将地址有效标誌位置位;这样,当相应的运算类指令执行完毕后不再马上写主存,而是先送入相应的后行写数据缓冲暂存器中,并置数据有效标誌位。控制器自动根据相应的后行写地址缓冲暂存器中的地址向主存发出写请求。

关键技术

採用先行控制技术的关键是缓冲技术和预处理技术。

1、缓冲技术:在工作速度不固定的两个功能部件之间设定缓冲栈,用以平滑功能部件之间的工作速度。

2、预处理技术:将进入运算器的指令均处理成RR型指令,而某些栈为其提供所需的运算元(先行读数栈、后续写数栈),这样运算器在进行预算时无需访问存储器,从而加快速度。

执行情况

在採用先行控制方式的处理机中,一个程式的执行情况如下表所示。

指令地址 | 指令执行情况 |

…… k-i-1 | 已经执行完成的指令 |

k-i …… k-1 | 在“后行写数栈”中等待把结果写到主存储器中的指令 |

k | 正在“指令执行部件”中执行的指令 |

k+1 …… k+j | 已经由“指令分析器”预处理完成,被存放在“先行操作栈”中的RR*型指令,指令所需要的运算元也已经读到“先行读数栈”中 |

k+j+1 …… k+j+n | 指令已经由“指令分析器”预处理完成,存放在“先行操作栈”中,指令所需要的运算元还没有读到“先行读数栈”中 |

k+j+n+1 | 正在“指令分析器”中进行分析和预处理的指令 |

k+j+n+2 …… k+j+n+m | 已经从主存储器中预取到“先行指令缓冲栈”中的指令 |

k+j+n+m+1 …… | 还没有进入处理机的指令 |

海之美文新闻资讯

海之美文新闻资讯