pstn网同步

滑码问题

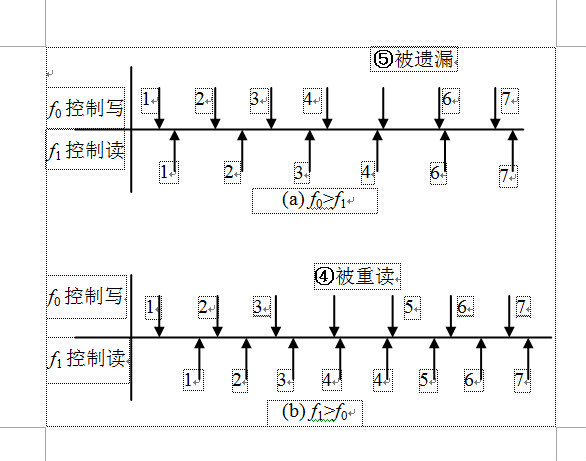

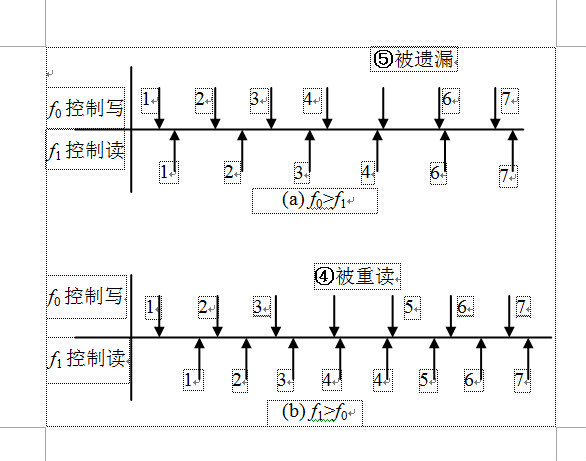

滑码是数字交换的一个特殊问题,其起因是两个数字交换局的频率不相等。图1是产生滑码的原理图。由图可见,当本局时钟频率f1低于入局时钟频率f0时,会不断产生遗漏一帧的情况(如第5次被遗漏)。如f1高于f0,会不断产生重读一帧的情况(如第4次被重读)。频率相差愈多,遗漏和重读发生得愈频繁。每发生一次遗漏或重读,就称为发生滑码一次。不同频率精度发生滑码的频繁程度见表1。滑码和失步是两个概念,不要混淆。在下面所述达到主从同步时,从理论上讲,是不会发生滑码的,但实际情况要複杂些,还会发生滑码。随着温度变化,线路延迟也会变化,数码会提前到来或推迟到来,这等效于频率变化,当积累至一定值时,就会发生滑码。

图1 滑码发生原理示意图

表1 振频精度和滑码发生对照表

码率(bit/s) | 频率精度 | 每天发生的滑码次数 | 每小时发生的滑码次数 | 发生一次滑码的间隔时间 | |

2×10 | 10 | 6.7×10次 | 2.8×10次 | 3.97年 | |

2×10 | 10 | 6.7×10次 | 2.8×10次 | 145天 | |

2×10 | 10 | 0.067次 | 2.8×10次 | 14.5天 | |

2×10 | 10 | 0.67次 | 0.028次 | 35小时 | |

2×10 | 10 | 6.72次 | 0.28次 | 12 800s | |

2×10 | 10 | 67.2次 | 2.8次 | 1 280s | |

2×10 | 10 | 672次 | 28次 | 128s | |

2×10 | 10 | 6 720次 | 280次 | 12.8s | |

一般程控交换机都具有滑码超过规定值时即告警的性能,如告警时能显示滑码的方向(重读或遗漏)则更佳。这个规定值应可通过人机通信加以改变。

滑码对通信的影响,是随着通信种类不同而各异的。在进行数据或图像传输时,滑码发生的后果很严重,但在通话时,滑码就不那幺严重了。有关资料表明,当频率差为10时,也就是大致上每小时出300次滑码时,才会在通话中听到“喀呖”声,使通话受到严重影响。

ITU-T已对滑码率的发生制定了详细的要求,将滑码率的发生分成四级,第一级是基本上无滑码,或滑码率少于70天一次;第二级是滑码率多于70天一次,少于5小时一次;第三级是滑码率多于5小时一次,少于2分钟一次;第四级是滑码率多于2分钟一次。上述第一级是质量非常高的通信;第二级是满意的;第三级质量低劣,通话尚可勉强进行,数传就不行了;第四级是完全不能接受的。在一年内,属于第四级的时间要少于0.1%,第三级要少于1%,第一和第二级要大于99%。应该注意,上面是端到端的指标。因一个通信要涉及许多交换局,因而每个交换局分配到的指标要比上面讲的还严格。

準同步和主从同步

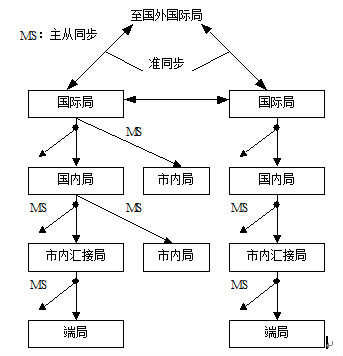

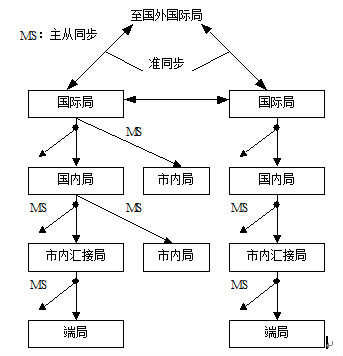

準同步和主从同步是解决网同步的两种方法。所谓準同步是各数字交换局在时钟上相互独立,毫无关联,但都具有极高的精度和稳定度,一般均採用原子钟。由于精度高,网内各局的时钟虽然并不完全相同,但误差很小,接近同步。这就是準同步的意思。所谓主从同步,是指网内设一主局,配有较高精度的时钟,网内其他各局均受控于该主局,并且逐级下控,直至终端局或远端集线器。图2是準同步和主从同步相结合的示意图,图中示出两个国际局,这两个国际局之间,以及其和国外的国际局之间,採用準同步。这两个国际局各控制一批国内、市内局。

图2 準同步和主从同步原理图

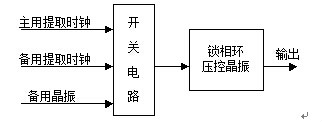

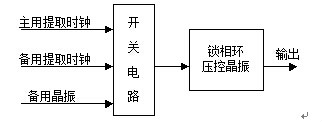

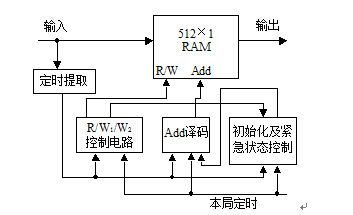

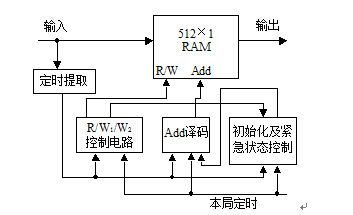

必须注意,在主局控制从局时,是控制整个从局的时钟。一般的做法是,在主局和从局之间选择主用路由和备用路由各一条,正常时由主用路由提取的定时去控制从局的锁相振荡器,当主用路由失效时,就由备用路由提取的定时来控制。当主、备路由都失效时,就由备用晶振来工作。这方面的安排见图3,为紧耦合主从同步。图4是另一种松耦合主从同步方框图。由图4可见,这种方式只要一个提取时钟进行控制,不需要备用的提取时钟,更不需要备用晶振。当输入的提取时钟正常时,控制器使相位调整、

图3 紧耦合主从同步示意图

图4 松耦合主从同步示意图

相位比较和开关等电路起作用,输入的提取时钟经分频后的信号,和高精度晶振输出经分频后的信号进行相位比较。比较后的误差输出通过开关,变换成数位讯号存入存储器,存储器的读出再变换成电压信号去控制高精度晶振,使高精度晶振的输出频率锁定于输入的提取时钟,以达到主从控制的目的。由上面的叙述可知,松耦合的控制原理和通常的锁相环相似,只不过中间增加了电压—数字变换以及数字—电压逆变换罢了。由于数位讯号(代表频率漂移)控制十分精细,所以松耦合主从控制的精度非常高。当输入的提取时钟失效时,通过故障检测电路,使控制器将开关电路等封闭,从而使存储器能保持失控时的值,也就是说有了“记忆”功能,因而也使高精度晶振输出维持原来的频率和相位。据称,松耦合主从控制可以达到几天内保持频率漂移小于10/天的水平,而在这期间输入的提取时钟总能修复的。由此可见,松耦合主从控制比紧耦合主从控制要优越得多。

对时钟的要求

时钟是数字程控交换机等设备的一个重要部件,它的好坏直接对网同步的各项技术指标发生影响,必须给予足够重视。

对时钟一般提出3个要求:第1个要求是精度,是指时钟频率相对于其标称频率的频率偏移绝对值的衡量,有一个最低準确度的要求,即最多允许的偏移。第2个要求是稳定度,是指在失去同步的情况下,时钟频率的变化,有一个最低稳定度的要求,即在一定时间内最多允许频率变化多少。第3个要求是牵引範围,即在有同步控制的情况下,能在多大的频率变化範围内仍能达到同步。

实际套用的时钟一般分为3个等级,即铯原子钟时钟,高稳定度晶振以及低稳定度晶振,它们的精度、稳定度和牵引範围分别如下所述。

铯原子钟时钟:在精度方面其最低準确度优于1×10,长期稳定性可达1×10/年,无牵引範围可言,因为这种钟是作为基準时钟,用于控制其他时钟的,不存在再受其他时钟控制的情况。

高稳定度晶振时钟:在精度方面其最低準确度一般在10~10之间,长期稳定性一般优于10/天,牵引範围一般在10~10範围。

低稳定度晶振时钟:在精度方面其最低準确度一般在10~10之间,长期稳定性优于10/天,牵引範围可在10~10之间。

一般铯原子钟只作为基準时钟用,因为它的价格非常高昂。省中心以上的长途局,特大城市和大城市的市话汇接局等可考虑採用高稳定晶振时钟;县中心局、小城市的长途局,一般市话端局以及再以下的局可考虑採用低稳定度晶振时钟;至于地区中心局,中等城市等局,可在高稳定性晶振和低稳定性晶振之间选用。随着技术的进步,电子设备和器件的不断降低价格,採用高稳定性晶振的场合越来越多。

同步网设备

上面所述的主从同步,原来都是採用提取定时的方法实现的,即在上级局至下级局的数字中继中,在到达下级局后进行定时提取,作为同步控制用。实践证明这种实现方法有些缺陷,主要是数字码流在传输过程中会发生一些漂移和抖动,这种漂移和抖动将对同步产生影响。随着传输距离延长,漂移和抖动将加剧,对同步产生的影响也加重。

为了解决这个问题,世界各国都发展了一些同步网设备,如美国的大楼综合定时系统(BITS),欧洲的同步供给单元(SSU)等,用了这些同步网设备后,就可取代定时提取而达到同步控制目的。实现的机理很简单,即在最高级设定稳定性非常高的时钟,用专用的传输链路逐级往下级的区域性基準钟或大楼综合定时系统送,在其中对收到的定时进行处理,除去漂移和抖动,获得良好的时钟,再输出到各种程控交换机等设备,进行同步控制,由于已经除去了漂移和抖动,使同步获得满意的效果。

我国已在全国建立同步网,全国最高级基準时钟PRC设在北京和武汉,各设一个铯原子钟和GPS(全球定位系统)接收机,其输出往下输送至区域基準时钟LPR。全国省中心以上城市各设一个LPR,在LPR中除接收PRC的时钟外,也设GPS接收机和一个铷原子钟(精度比铯原子钟稍差)。LPR的时钟再输出至下级的BITS,BITS的输出就可供给各种程控交换机等设备作为同步控制用了。用了BITS的控制后,原来的定时提取控制就可不用,同步效果得到很大的改善。在某些场合,BITS输出一时不能到达,或在距离较近的市(县)内某些局之间,仍可使用定时提取的同步控制方法。

帧同步和弹性存储器

一个交换局往往用很多个E1连线至不同的交换局,这些E1的2Mbit码流在到达此交换局后,在时间上往往是对不齐的,如图5所示,在本局帧结构的TS0时间,第一个E1的时间是在TS5,另一个E1的时间是在TS19,等等,因为这个交换局和各局的距离不同,时延也不相同,各局的帧结构本来也是各自独立产生的,因此造成如图5所示的情况是十分正常的。帧同步的目的就是要解决各个E1的码流到达后和本局的帧结构对齐。

图5 各局码流和本局帧不同步示意图

早期的数字程控交换机採用可控延线来解决帧同步问题。每个E1终端需装可控延迟线一个。可控延迟线提供的最大延迟是125µs,在提取的外界TS0和本局TS0比较下,可控延迟线由伺服马达控制提供适当的延迟,使外界码流抵达数字交换网时,恰巧和本局定时对齐而达到帧同步。当外界TS0和本局TS0相差有变动时,随时调整延迟以保持同步。

后来出现了由可控移位暂存器或随机存储器实现的弹性存储器。採用移位暂存器实现弹性存储器时,每移1bit,延迟0.488µs (2Mbit码流时),则移位256bit就等于提供约125µs延迟了。如果弹性存储器由256bit可控移位暂存器组成,并可在外界TS0和本局TS0的相差控制下,自动提供0~255bit间任何比特的移位,则其作用原理和可控延迟线完全相同。

图6示出一个由双帧RAM实现的弹性存储器,RAM的容量是512×1。输入信息在提取的定时控制下存入RAM;然后在本局的定时控制下,从RAM读出。

弹性存储器统一由本局定时读出,不论外界提取的定时发生在什幺时间,显然均能达到帧同步。弹性存储器的关键是儘可能使本局定时和提取定时相差更多的时间,图6中的初始化及紧急状态控制电路能在弹性存储器刚开始工作时使本局定时和提取定时相差一帧时间。但是由于提取时钟和本局时钟的频率不可能完全相同,随着时间的推移,本局定时和提取定时将趋于接近,而产生滑码。图6中的初始化及紧急状态控制电路可在发生滑码时,立即将本局定时和提取定时拉开一帧的距离,这就减少或避免了滑码的发生及其对通信质量的影响。

图6 双帧RAM实现的弹性存储器原理图

海之美文新闻资讯

海之美文新闻资讯